# P1 课上测试游记

这次确实是差点翻车了,天知道为啥卡我半小时的竟然是第一题,后面两题加一起用的时间差点还没第一题多

通过阅读本文,您可以大致了解 2021 年秋季北航计算机组成课程 P1 课上测试的题目内容、难度和解题思路

P1 课上测试的主要内容是 Verilog 语言设计组合逻辑电路和有限状态自动机

题目每年都会发生变化,题意描述大致清晰,但是可能与原题有一定差异

本次课上确实挺危险,因为第一题不知为啥卡了将近 40min,还好状态机写的比较快,最后 1.5h 解决战斗,下面是回顾的题目大意

# T1 奇偶校验

输入一个 32 位的二进制数据,再用一位输入告诉你是要做奇校验还是偶校验,输出完成奇偶校验后的二进制数据,本题中最高位即第 31 位为奇偶校验位

所谓奇偶校验,就是检验数据中 1 的个数是奇数个还是偶数个,如果与要求不符,则通过改变最高位使数据符合要求

记得应该是 funct 为 0 时偶校验,为 1 时奇校验(反正无所谓,题意最重要)

| 端口名称 | 输入端 / 输出端 | 长度 |

|---|---|---|

| data | I | [31:0] |

| funct | I | [0:0] |

| result | O | [31:0] |

正解应该是将 data 的进行按位异或,结果是 1 就是奇数个 1,为 0 是偶数个 1,然后根据这个结果去改变 result[31] 的值

其实可以设一个计数器 cnt,遇到 1 加一,然后判断是不是偶数,但是我考场上脑子抽了,以为组合逻辑没法把 cnt 清零,因此卡了半天,等到仿佛全世界都过了 T1,当时确实心里非常慌... 可以说差点栽在 T1 上了

# T2 心情电路

题目描述挺复杂,而且没有形式化的题面,根据往年经验,T2 貌似都是描述很复杂的状态机,2020 年好像是炒菜啥的,但是写起来出人意料的简单,下面尝试描述一下题意

下面的题意记的不是很清楚,不一定正确

有 5 个状态,已经给你标好了序号,分别是 ASLEEP (000),BUSY (001),SAD (010),CLUELESS (011),HAPPY (100)

有 4 种不同的输入,也已经给你标好了序号,分别是 ALARM,FAIL,SUCCESS,IDEA

当你在做计组题目时:

- 如果你是 ASLEEP 状态,ALARM 会把你吵醒,你会变成 BUSY 状态

- 如果你是 BUSY 状态,FAIL 会让你变成 SAD 状态,SUCCESS 会让你变成 HAPPY 状态;

- 如果你连续 BUSY3 个时钟周期,你会回到 ASLEEP 状态;

- 如果你是 CLUELESS 状态,IDEA 会让你变成 BUSY 状态;如果你连续 CLUELESS3 个时钟周期,你会变成 ASLEEP 状态

- 如果你连续 SAD2 个时钟周期,你会变成 CLUELESS 状态

以上时钟周期不包括边界

| 端口名称 | 输入端 / 输出端 | 长度 |

|---|---|---|

| sign | I | [1:0] |

| clk | I | [0:0] |

| reset (异步复位) | I | [0:0] |

| status | O | [2:0] |

对,只需要知道大概题目有这么复杂就行了,但是根据题目画出状态转移图,搭一个 Moore 机,想做对挺容易,并没有啥技巧

# T3 字符串匹配

这次要匹配的字符串是一个方程的形式,大致要求如下

- 一个数字

[0-9]是一个表达式 - 一个字母

[a-zA-Z]是一个表达式 - 表达式之间用

'+' | '-' | '*' | '/'连接起来仍然是表达式 - 表达式与另一个表达式之间用

'='连起来得到方程 - 两个字符之间可以有任意多个空格,当然也可以没有

举例说明: 1+2=a+b 是一个方程, 1++=b 不是, +a+b=1+2 不是方程

| 端口名称 | 输入端 / 输出端 | 长度 |

|---|---|---|

| in | I | [7:0] |

| clk | I | [0:0] |

| reset (异步复位) | I | [0:0] |

| out | O | [0:0] |

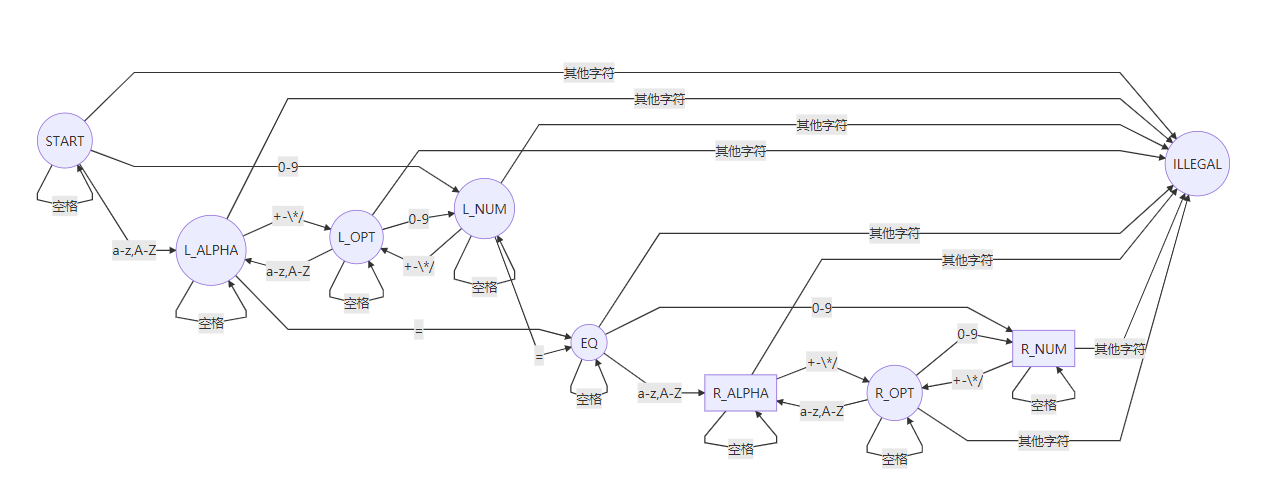

写了一个非常大的 Moore 机,有 START,L_NUM,L_OPT,L_ALPHA,EQ,R_NUM,R_OPT,R_ALPHA,ILLEGAL 九个状态,转移也不难写出(倒是下面这个图挺难画的)

然后 Verilog 写出来就好了

# Extra 附加题

两个附加题我都错了,还好附加题都不算分

附加题 1 是选择题,找 bug,题目是字符串识别 [a-zA-Z]+[._]{1}[0-9]+ ,然后找的时候细心点,反正我就随便来,最后漏选了

附加题 2 是填空题,题目挺有新意,让你根据波形图补全状态机的代码,我认真算了一会,交了两遍都错了,最后一看是要填十进制数字,结果我填的二进制,没看清题目倒霉... 下次记得看清楚 2'd__ 是填一个十进制数字,而不是填两个二进制数字...

# 助教提答

前几次的提答都挺水的,这一次检查了 testbench 的写法,问了一下什么是时钟信号,什么是测试信号,问了如何控制同步异步复位,还有问了 T3 的思路