# Logisim 复习

# 常见元件和门级电路

# Splitter(分路器)

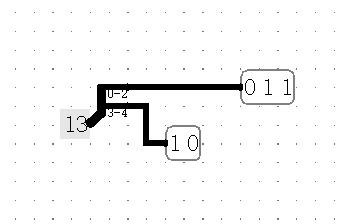

对于 0x13 来说,化为二进制数字是,这时分路器虽然显示的是 0-2 和 3-4 ,但是实际的显示顺序是从高位到低位,即 2-0 和 4-3 ,这和 Verilog 中的 wire[4:0] 的方向是一致的

分路器的位数就是字面位数,第 0 位是最右边,第 n 位是最左边(最高位)

分路器可以调节多种外观,而且未必需要用到所有位的数据,因此对于 [31:0] 的数据,如果我们想要 [21:15] 和 [21:11] 这时可以开两个分路器,每个分路器的 Fan out 属性设为 0

# Tunnel(隧道)

Tunnel 很好用,但是不能乱用,否则会使得电路很难懂

目前为止,我只在寄存器堆的搭建使用过 Tunnel ,记得 Label 的名字一定要规范

# 练习:搭建 swap 电路

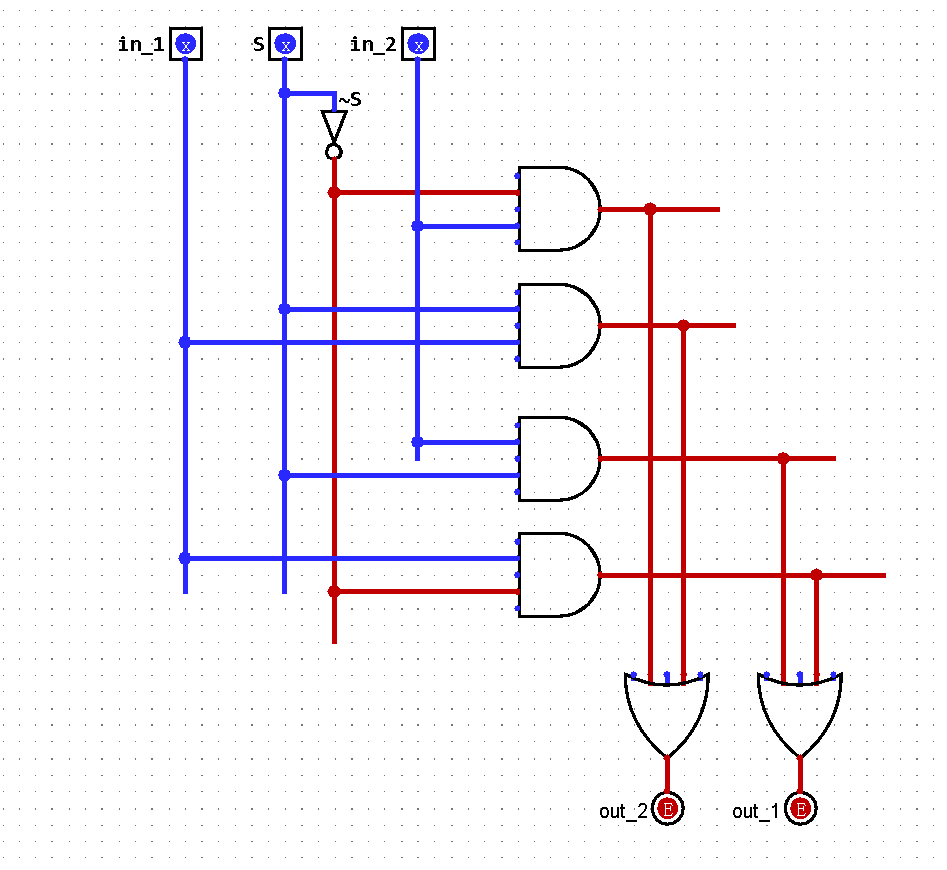

现在需要你使用基础的门电路搭建这样一个电路,当输入 S 为 0 (低电平)时,输出 O1 等于输入 I1 ,输出 O2 等于输入 I2 。当输入 S 为 1 (高电平)时,则交换两输出,即输出 O2 等于输入 I1 ,输出 O1 等于输入 I2 。我们给它取名叫做 swap 电路。

本题显然需要我们用组合逻辑实现,可以采用 Combinational Analysis 菜单直接输入真值表生成电路,如下图:

# 往年 Pre 考试题:判断假期

一年中有 1,4,5,6,9,10 月份有假期,输入月份(4 位 2 进制),判断有无假期

显然可以直接真值表生成组合逻辑来做,属于签到题

# 组合逻辑电路及部分原件

# 子电路

子电路的外观一定要和题目要求保持一致,否则会出问题,另外命名也要注意,如果不小心输入错了可以去 Circuit Name 一栏去改

另外貌似 Logisim 不能把整个子电路给复制一遍...(但是通过复制 VSCode 打开的 ).xml 的源文件可以,但是很容易复制错,建议先把要复制的文件设为 main ,然后复制到 </circuit> ,最后记得加上 </project>

# 多路选择器、译码器和多路分配器

这三者都在

Plexers菜单里面

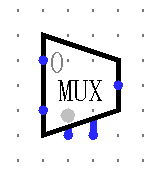

# 多路选择器(Multiplexer)

带灰色小圆点的那个端口是选择信号输入端口,待选择信号从灰色的 0 开始依次向下或者向上递增,如果是 2 位选择信号那从上到下就是 00,01,10,11

下面的另一个输入的是 1 位使能信号,如果设置 Disabled Output 是 Floating ,那么使能信号置为 0 时,输出始终为 x ,如果设置为 Zero ,那么使能信号置为 0 时,输出始终为 0,使能信号为 1 时按照选择信号输出

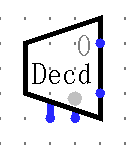

# 译码器(Decoder)

最显著的特点就是没有输入信号,按照灰色小圆点输入的选择信号将相应的端口置为 1,其余端口如果设置 Disabled Output 是 Floating 那就是 x ,否则就是 0

# 多路分配器(Demultiplexer)

多路分配器和多路选择器功能恰好相反,即能够将 1 个输入数据,根据需要传送到多个输出端的任何一个输出端

# 时序电路

# SR 锁存器、D 锁存器、D 触发器

要点:

- SR 锁存器的 S 和 R 不能同时置为 1,S 为 1 代表写入 1,S 为 0 写入 0,R 是 reset 代表复位,S 和 R 同时为 0 则值不变

- D 锁存器在 SR 锁存器的基础上进行修改,加入 CLK 时钟信号,在 CLK=1 时,D 的输入有效,否则原输入值不变

- D 触发器是两个 D 锁存器背靠背连在一起,CLK=0 时,主锁存器透明,数据进入主锁存器,但是从锁存器封闭,数据无法进入,当 CLK=1 是,从锁存器透明,数据从主锁存器流入从锁存器,但是主锁存器不透明,因此相当于在时钟周期上升沿将数据从 D 流入 Q

# 寄存器

D 输入,Q 输出,三角为时钟信号,左侧蓝点为使能端,不输入或者输入 1 表示启用寄存器,否则保持原有值不变,下面蓝点代表 reset

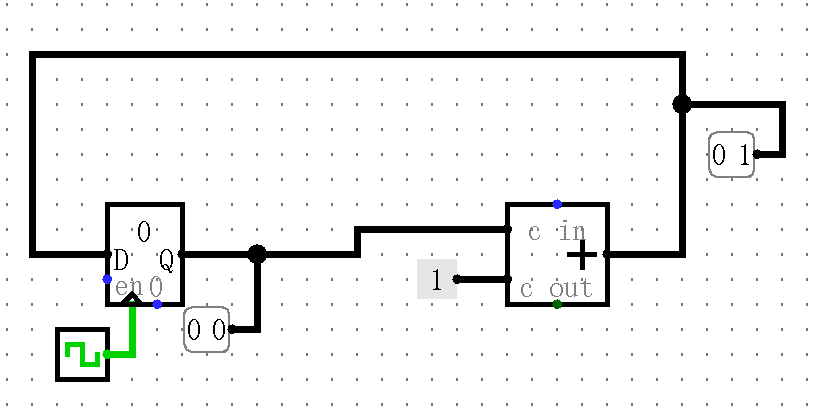

通过这个电路,理解寄存器内部的工作原理

# 有限状态机

搭建状态机,首先要设计状态,常见的有后缀自动机,AC 自动机,自动售货机,这些的状态的确定有一定套路

有限状态机由计算 next_state 的状态转移电路,储存当前状态 (state) 的寄存器,输出部分电路三部分组成,状态转移和输出都是组合逻辑电路